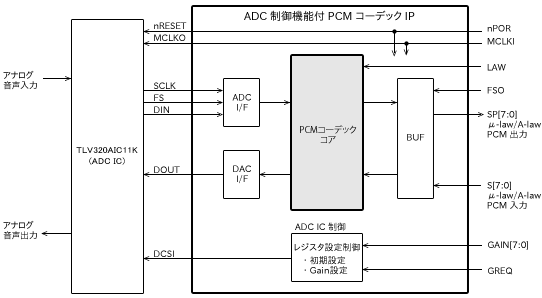

ADC制御機能付PCMコーデック(音声コーデック)

本製品は、Texas Instruments製ADC IC(TLV320AIC11K)との組み合わせにより実現した、FPGA用のPCMコーデックIPです。

特長

- ITU-T G.711準拠

- リニアPCM ⇔ μ-law/A-law PCM変換

- TLV320AIC11K内蔵の音声帯域フィルタ回路を利用

ブロック図

インタフェース

※I/OはFPGAブロックから見た入出力方向

| 信号名 | I/O | 機能 | |

|---|---|---|---|

|

※1 ゲイン設定(ADCゲイン/DACゲイン共通) 0:0dB、1:-36dB、2:-30dB、3:-24dB、4:-18dB、5:-12dB、6:-9dB、7:-6dB、8:-3dB、9:+3dB、10:+6dB、11:+9dB、12:+12dB、13:+18dB、14:+24dB、15:MUTE | |||

| MCLKI | I | マスタクロック入力 | |

| MCLKO | O | マスタクロック出力 | |

| nPOR | I | リセット入力(0:リセット) | |

| nRESET | O | リセット出力(0:リセット) | |

| ADC I/F | SCLK | I | シリアルクロック入力 |

| FS | I | フレーム同期入力(SCLK同期) | |

| DIN | I | ADC データ入力 | |

| DAC IF | DOUT | O | DACデータ出力 |

| PCM | LAW | I | Law 設定入力(0:μ-law/1:A-law) |

| FSO | I | フレーム同期入力(MCLK_I 同期) | |

| SP[7:0] | O | μ-law/A-law PCM データ出力(MCLK_I 同期) | |

| S[7:0] | I | μ-law/A-law PCM データ入力(MCLK_I 同期) | |

| ゲイン制御 | GREQ | I | ゲイン設定変更時”H”入力(MCLK_I同期) |

| GAIN[7:0] | I | ゲイン設定入力(MCLK_I同期) [7:4]=ADCゲイン設定/[3:0]=DACゲイン設定 ※1 | |

| DCSI | O | レジスタ制御データ出力 | |

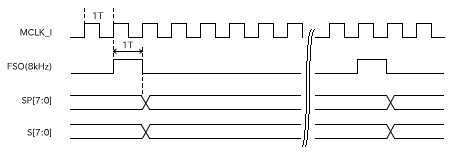

タイミングチャート

PCMデータ出力インタフェース タイミングチャート

※1 FSO、SP[7:0]、S[7:0] はMCLK_I同期の信号とします。

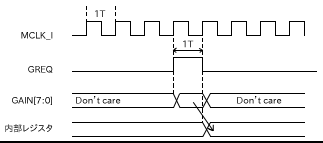

Gain制御インタフェース タイミングチャート

※2 GREQ、及び、GAIN[7:0] はMCLK_I 同期の信号とします。

※3 MCLK_I 立ち上がり時にGREQがHighならば、GAIN[7:0]を内部レジスタに取り込んで、その後Gain設定制御を開始します。

規模(参考)

| FPGAデバイス | ALTERA製 CycloneIII(EP3C10) |

|---|---|

| 使用LE数 | 約1,300LEs |

| メモリ使用量 | 0 |

| ※ その他デバイスの対応に関してはお問い合わせください。 | |

ご提供方法

- ご要望により本IPコアのカスタマイズおよび機能を追加してのご提供も可能です。

- 外部制御回路等の周辺回路のカスタム設計も承りますので、ご相談ください。

- Verilog-HDL 言語で設計しています。(VHDL 言語での対応についてはご相談ください。)

- マクロ(ネットリスト)によるご提供やROM 形式でのご提供も可能です。